Nuevos Chips de IBM para Inteligencia Artificial

Keypoints:

- 1. Los nuevos chips prototipo de IBM Research utilizan mucha menos energía para tareas de IA, lo que es esencial para reducir la huella de carbono de la IA.

- 2. Los chips analógicos de IBM pueden realizar tareas de reconocimiento y transcripción de voz de manera eficiente en términos energéticos, consumiendo menos energía que los dispositivos digitales comparables.

- 3. El diseño de chips analógicos de IBM puede codificar hasta 17 millones de parámetros, lo que permite abordar experimentos de IA de manera efectiva.

L os Nuevos Chips Prototipo de IBM Research Utilizan Drásticamente Menos Energía para Resolver Tareas de IA.

Los Nuevos Chips Prototipo de IBM Research Utilizan Drásticamente Menos Energía para Resolver Tareas de Inteligencia Artificial.

En un artículo publicado en la revista Nature, IBM mostró que es posible construir chips de IA analógicos que pueden manejar tareas de IA de lenguaje natural con una eficiencia energética estimada 14 veces mayor.

El Interés de IBM en la Inteligencia Artificial

Aunque aún estamos en el umbral de la revolución de la IA, la inteligencia artificial ya ha comenzado a revolucionar la forma en que vivimos y trabajamos. Sin embargo, hay un problema: la tecnología de IA consume una cantidad increíble de energía. Según algunas estimaciones, ejecutar un modelo de IA grande genera más emisiones a lo largo de su vida útil que el automóvil promedio estadounidense.

El futuro de la IA requiere nuevas innovaciones en eficiencia energética, desde la forma en que se diseñan los modelos hasta el hardware que los ejecuta. Y en un mundo cada vez más amenazado por el cambio climático, cualquier avance en la eficiencia energética de la IA es esencial para mantenerse al día con la huella de carbono en rápida expansión de la IA.

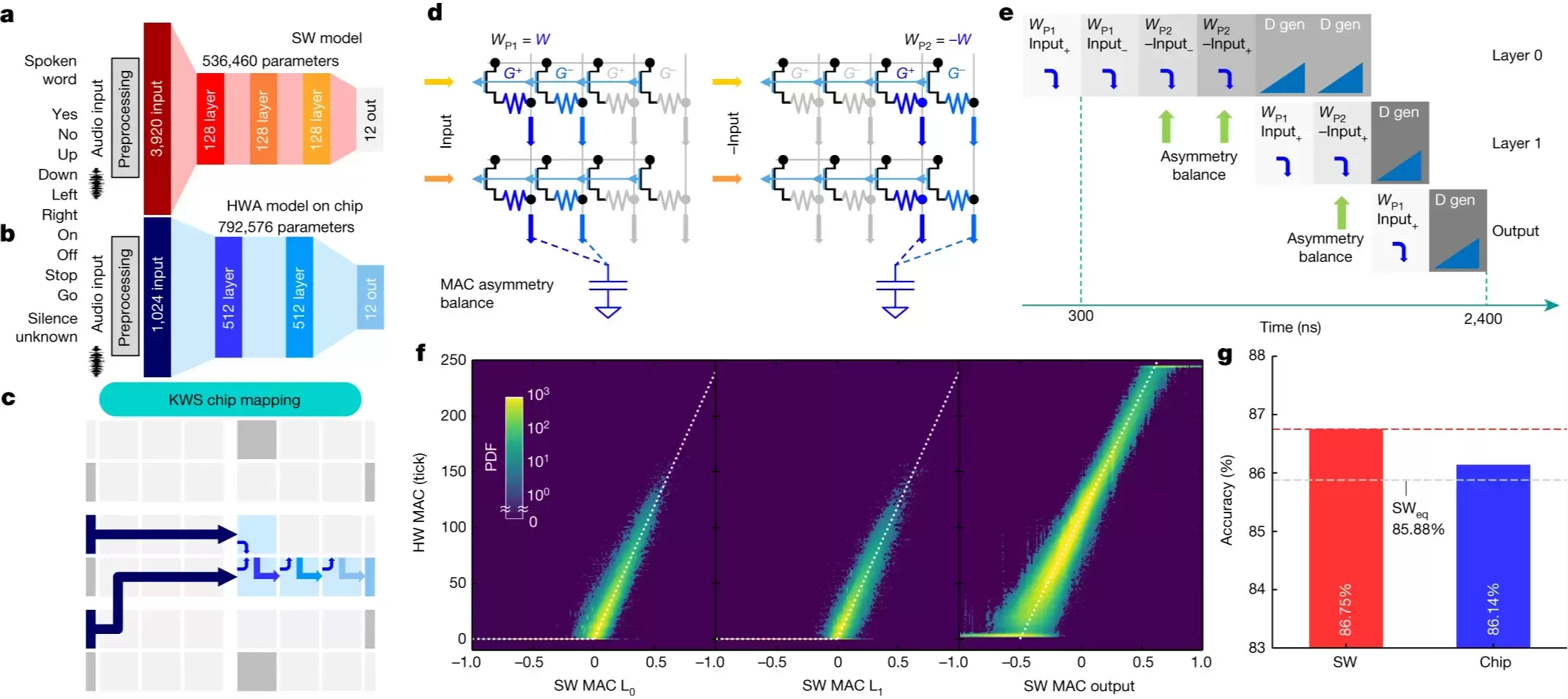

Y uno de los últimos avances en eficiencia de IA de IBM Research se basa en chips analógicos, que consumen mucha menos energía. En un artículo publicado en Nature hoy, investigadores de laboratorios de IBM de todo el mundo presentaron su prototipo de chip de IA analógico para el reconocimiento y la transcripción de voz eficientes en términos energéticos. Su diseño se utilizó en dos experimentos de inferencia de IA, y en ambos casos, los chips analógicos realizaron estas tareas tan confiablemente como los dispositivos completamente digitales comparables, pero terminaron las tareas más rápido y consumieron menos energía.

El concepto de diseñar chips analógicos para inferencia de IA no es nuevo: los investigadores han estado contemplando la idea durante años. En 2021, un equipo en IBM desarrolló chips que utilizan memoria de cambio de fase para codificar los pesos de una red neuronal directamente en el chip físico. Pero investigaciones anteriores en el campo no habían mostrado cómo se podrían utilizar chips como estos en los modelos masivos que vemos dominar el panorama de la IA hoy en día. Por ejemplo, GPT-3, uno de los modelos populares más grandes, tiene 175 mil millones de parámetros o pesos.

El diseño que el equipo de IBM Research ha creado puede codificar 35 millones de dispositivos de memoria de cambio de fase por chip; en otras palabras, modelos con hasta 17 millones de parámetros. Aunque esto aún no se compara con el tamaño de los modelos generativos de IA de vanguardia de hoy, combinar varios de estos chips les ha permitido abordar experimentos en casos de uso reales de IA de manera tan efectiva como los chips digitales podrían hacerlo.

El enfoque que tomó el equipo fue optimizar las operaciones de multiplicación-acumulación (MAC) que dominan el cálculo de aprendizaje profundo. Al leer las filas de una matriz de dispositivos de memoria no volátil resistivos (NVM) y luego recopilar corrientes a lo largo de las columnas, el equipo demostró que pueden realizar MAC dentro de la memoria. Esto elimina la necesidad de mover los pesos entre la memoria y las regiones de cálculo de un chip o entre chips. Los chips analógicos también pueden llevar a cabo muchas operaciones MAC en paralelo, lo que ahorra tiempo y energía.

El concepto analógico tiene un gran potencial, pero también hay desafíos significativos para el diseño y la fabricación de chips: la informática analógica es inherentemente imprecisa, se deben desarrollar nuevos procesos para producir NVM de alto rendimiento a gran escala y para conectar chips analógicos a sistemas digitales tradicionales. Pero el trabajo que los investigadores de IBM han realizado señala un futuro en el que estos chips podrían ser potencialmente tan útiles como los chips digitales.

Pruebas de hardware de IA analógico

El equipo de IBM Research diseñó dos experimentos para probar la eficacia de sus diseños. El primero giraba en torno a la detección de palabras clave. De la misma manera en que esperarías que tu altavoz inteligente respondiera si dijeras en voz alta "Hola Siri" o "Hola Google", el equipo quería ver si podían usar su diseño de chip para reconocer palabras habladas específicas. Crearon un sistema que escuchaba 12 palabras, y en cada caso, el chip analógico podía reaccionar a cada palabra con la misma precisión que los sistemas basados en software que existen hoy en día, pero considerablemente más rápido. Los sistemas que esperan y escuchan una palabra clave específica hoy en día requieren energía para esperar inactivos, mientras que el diseño que creó el equipo puede apagarse cuando no se necesita, ya que los pesos del modelo se almacenan en el chip, en memoria no volátil.

Usando modelos cargados en MLCommons, un sitio de benchmarking y colaboración de la industria, el equipo pudo comparar la eficacia de su sistema de demostración con los que se ejecutan en hardware digital. Desarrollado por MLCommons, el repositorio de datos de benchmark MLPerf mostró que el prototipo de IBM fue siete veces más rápido que la mejor presentación de MLPerf en la misma categoría de red, manteniendo una alta precisión. El modelo se entrenó en GPUs utilizando un entrenamiento consciente del hardware y luego se implementó en el chip de IA analógico del equipo.

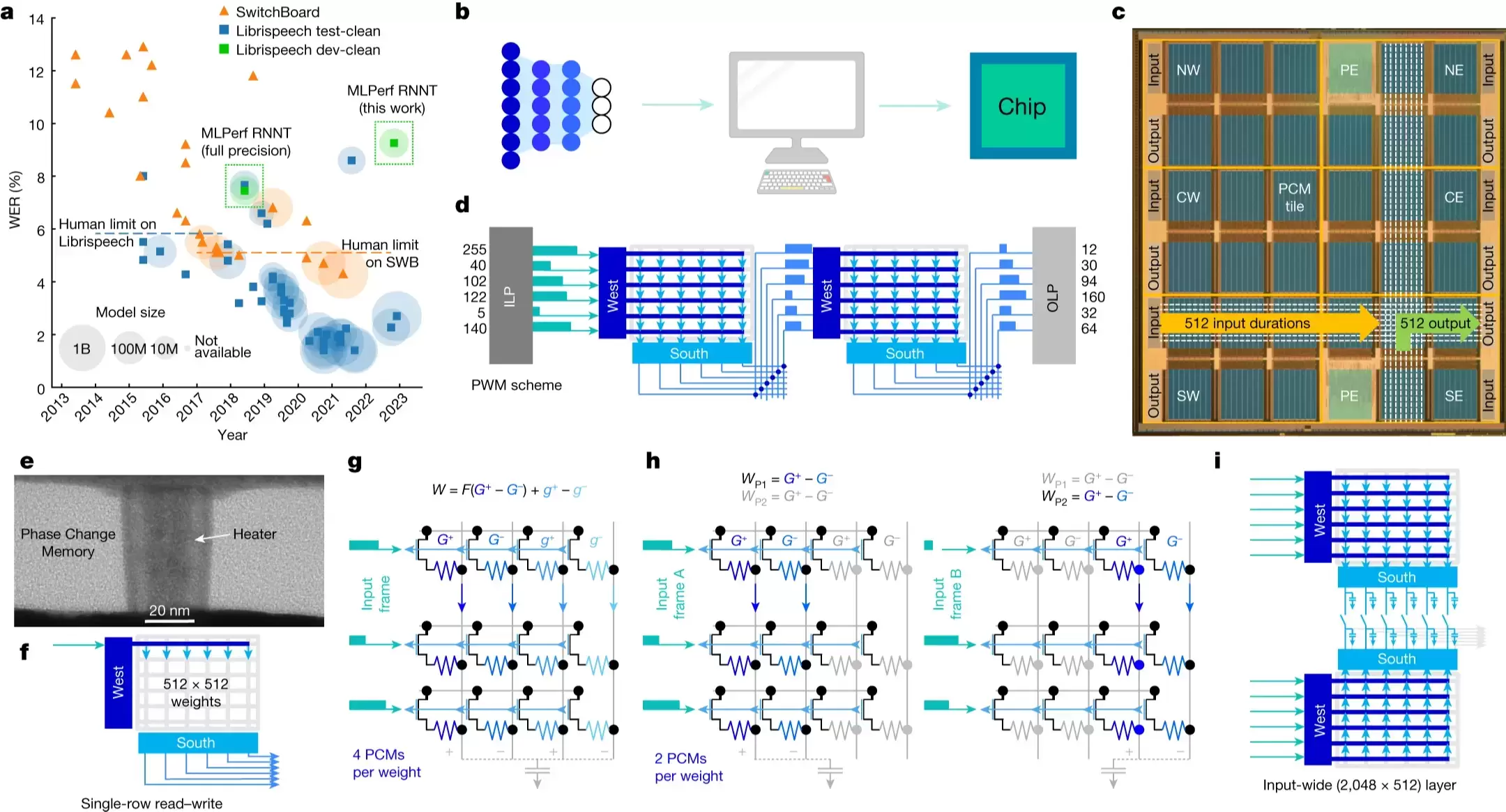

El segundo experimento fue considerablemente más grande e insinúa un futuro en el que los sistemas de IA generativos, construidos sobre chips analógicos, podrían usarse en lugar de los digitales. El objetivo era implementar un modelo grande y complejo, utilizando cinco de los chips del equipo ensamblados, y realizar cálculos digitales simulados fuera del chip para mostrar la escalabilidad de la IA analógica. Los investigadores ejecutaron un modelo de red neuronal recurrente transductor (RNNT) de habla a texto que se encuentra en MLPerf para transcribir, letra por letra, lo que una persona está diciendo. Las RNNT son populares para muchas aplicaciones del mundo real en la actualidad, como asistentes virtuales, búsqueda de contenido multimedia y sistemas de subtitulado, y documentación y dictado clínicos.

El sistema contenía 45 millones de pesos en 140 millones de dispositivos PCM en cinco chips. Fue capaz de tomar el audio de personas hablando y transcribirlo con una precisión muy cercana a las configuraciones de hardware digital. A diferencia de la primera demo

stración, esta no fue completamente de extremo a extremo, lo que significa que sí requería cierto cálculo digital fuera del chip. Sin embargo, la cantidad de cómputo adicional involucrado aquí es tan pequeña que, de haberse implementado en el chip, la eficiencia energética resultante aún sería mayor que la de los productos en el mercado actual.

Nuevamente, utilizando datos cargados en MLCommons, el equipo comparó la eficacia de su red con RNNT que se ejecutan en hardware digital. Los datos de MLPerf mostraron que se estima que el prototipo de IBM es aproximadamente 14 veces más eficiente por vatio, o eficiente, que los sistemas comparables. Este es el primer sistema analógico que los investigadores de IBM han podido probar con MLPerf, ya que los experimentos anteriores simplemente eran demasiado pequeños para comparar.

¿Qué sigue para la IA analógica?

Las tareas de lenguaje natural no son los únicos problemas de IA que la IA analógica podría resolver: los investigadores de IBM están trabajando en una serie de otros usos. En un artículo publicado a principios de este mes en Nature Electronics, el equipo mostró que era posible utilizar un diseño de chip analógico eficiente en energía para una arquitectura escalable de señal mixta que puede lograr una alta precisión en el conjunto de datos de imágenes CIFAR-10 para el reconocimiento de imágenes de visión por computadora.

Estos chips fueron concebidos y diseñados por investigadores de IBM en los laboratorios de Tokio, Zúrich, Yorktown Heights, Nueva York y Almaden, California, y construidos por una empresa de fabricación externa. La memoria de cambio de fase y los niveles de metal fueron procesados y validados en el laboratorio de IBM Research en el Albany Nanotech Complex.

Si combináramos los beneficios del trabajo publicado hoy en Nature, como las matrices grandes y el transporte de datos paralelo, con los bloques de cálculo digital capaces del chip mostrado en el artículo de Nature Electronics, veríamos muchos de los componentes necesarios para realizar la visión de un acelerador de inferencia de IA analógica rápida y de baja potencia. Y al emparejar estos diseños con algoritmos de entrenamiento resistentes al hardware, el equipo espera que estos dispositivos de IA entreguen la equivalencia de software de precisión de redes neuronales para una amplia gama de modelos de IA en el futuro.

Si bien este trabajo es un gran avance para los sistemas de IA analógica, aún queda mucho por hacer antes de que podamos ver máquinas que contengan este tipo de dispositivos en el mercado. El objetivo del equipo en el futuro cercano es combinar los dos flujos de trabajo mencionados en un solo chip mixto analógico, el equipo también está buscando cómo se podrían implementar modelos base en sus chips.

La IA analógica está ahora en el camino para resolver los tipos de problemas de IA que los sistemas digitales actuales están abordando, y la visión de la IA analógica consciente de la energía, junto con los sistemas digitales que usamos hoy, se está volviendo más clara.

Share Share Share

(0) Comments

More from @digitalcori for #OlaGG

View MoreRyan Cohen de GameStop Cree que las Unidades de Disco Deben ser Obligatorias para las Consolas

over 2 years ago

5 views

Sorare Lanza una Búsqueda del Tesoro Global de Cartas 3D con Premio del AC Milan

over 2 years ago

5 views